# **EXHIBIT J**

# U.S. Patent No. 7,009,226

# TSMC Products (TSMC 28nm LP and 40nm Technology nodes)

"1. A semiconductor device comprising:"

1. A semiconductor device comprising:

Integrated circuits fabricated by TSMC in its 28nm LP or 40nm technology nodes (the "TSMC Products") include a semiconductor device.

For example, the Qualcomm MSM8952 integrated circuit (the "Qualcomm Chip") is an exemplary TSMC Product.

See e.g., TSMC28LP\_001.

The Qualcomm Chip is manufactured using TSMC's 28nm LP technology node.

# Qualcomm Snapdragon 617 MSM8952

The **Qualcomm Snapdragon 617 MSM8952** is a midrange ARMv8-based SoC largely for Android tablets and smartphones announced in September 2015. In addition to 8 Cortex-A53 CPU cores at up to 1.5 / 1.2 (performance and

power saving cluster) GHz, the SoC integrates an Adreno 405 GPU with a LPDDR3-1866 memory controller and supports Wi-Fi (802.11ac), Bluetooth 4.0, UMTS, and LTE. Compared to the older Snapdragon 615, the clock speeds are a bit lower (hits 1.7 GHz max).

See e.g., https://www.notebookcheck.net/Qualcomm-Snapdragon-617-MSM8952-SoC.156364.0.html.

"1. A semiconductor device comprising:"

### **Power Consumption**

The Snapdragon 617 is manufactured by TSMC in a 28 nm LP process. According to the specifications, we expect a medium or medium-high power consumption for use in medium-sized or larger smartphones and tablets.

See e.g., https://www.notebookcheck.net/Qualcomm-Snapdragon-617-MSM8952-SoC.156364.0.html.

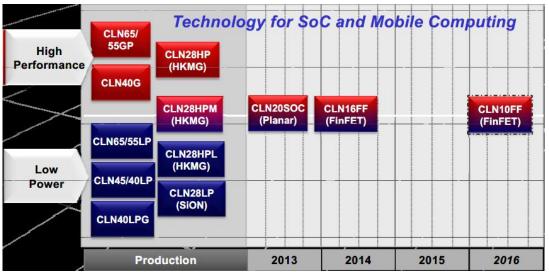

TSMC's 28 nm technology platform is offered in four variants, denoted High Performance (HP), High Performance Mobile Computing (HPM), High Performance Low Power (HPL), and Low Power (LP). The LP technology node uses the SiON/Poly-Si gate stack.

*See* Henry Hsieh, TSMC Technology and Innovation Platform for Mobile Computing (Nov., 2012), p.3, *available at* <a href="http://www.armtechforum.com.cn/2012/10">http://www.armtechforum.com.cn/2012/10</a> TSMC.pdf; TSMC, TSMC 28nm Technology in Volume Production, *available at*

https://www.tsmc.com/uploadfile/ir/BusinessRelease/20111024161709877\_sw3I/Oct24\_2011\_E.pdf.

TSMC's 28nm LP technology node is essentially a die shrink of TSMC's 40nm LP technology node.

# Case 1:19-cv-00308-MN Document 1:19. 7, 19. 7, 19. 22/13/19. 1 Page 5 of 17 PageID #: 187

"1. A semiconductor device comprising:"

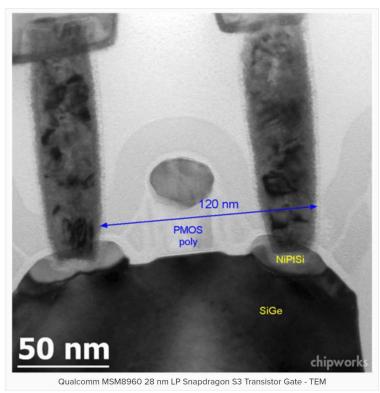

The minimum contacted gate pitch was 120 nm. The 28 nm LP process is essentially a shrink of TSMC's 40 nm LP process (with the addition of the e-SiGe for PMOS), which was (notably) used to fabricate the NVIDIA Tegra T20-H-A2 application processor. The 40 nm LP process featured a 160 nm contacted gate pitch in the logic regions.

*See e.g.*, <a href="https://www.chipworks.com/about-chipworks/overview/blog/review-tsmc-28-nm-process-technology">https://www.chipworks.com/about-chipworks/overview/blog/review-tsmc-28-nm-process-technology</a>.

"1. A semiconductor device comprising:"

# 40 nm

*See e.g.*, TechInsights, Logic Roadmap, p.7, <a href="https://www.techinsights.com/techservices/TechInsights-Logic-Roadmap-2016.pdf">https://www.techinsights.com/techservices/TechInsights-Logic-Roadmap-2016.pdf</a>.

Accordingly, the structure, function, operation, and implementation of integrated circuits fabricated on TSMC's 28nm LP technology node are substantially similar to the structure, function, operation, and implementation of integrated circuits fabricated on TSMC's 40nm technology node.

The TSMC Product comprises a semiconductor device. For example, the Qualcomm Chip includes a semiconductor device.

## Case 1:19-cv-00308-MN Document 1:19 7- Filed 22/13/11:91 Page 7 of 17 PageID #: 189

"1. A semiconductor device comprising:"

TSMC was founded in 1987 and is the world's largest foundry with 2011 revenues reaching \$14.5 billion. According to their web site their total manufacturing capacity in 2011 was 13.2 million eight-inch wafer equivalents. They presently offer the full range of CMOS technologies from >0.5 µm down to 28 nm.

The 28 nm technology platform appeared in production in 2010 and is offered in four process variants, denoted HP, HPM, HPL and LP. We have analyzed three of these process variants to date, namely HP, HPL and LP. The 28 nm generation was the first time TSMC used high-k metal gate (HKMG) transistors. The HP and HPL technologies feature HKMG transistors, while the LP uses conventional poly gates, with an ONO gate dielectric. TSMC claims that their 28 nm process technology entered production in 2010; however, production devices were not available for analysis until mid-2011.

| Standard Offerings |              | HP   | HPM | HPL | LP   |

|--------------------|--------------|------|-----|-----|------|

| Core Vcc (V)       |              | 0.85 | 0.9 | 1.0 | 1.05 |

| VT                 | Ultra-Low    | ~    | ~   | ~   |      |

|                    | Low          | ~    | ~   | ~   | ~    |

|                    | Standard     | ~    | ~   | ~   | ~    |

|                    | High         | ~    | ~   | ~   |      |

|                    | Ultra-High   |      | ~   |     |      |

| 1.8V I/O           | 1.8V UD 1.2V | ~    | ~   |     | ~    |

|                    | 1.8V UD 1.5V | ~    | ~   | ~   | ~    |

|                    | 1.8V         | ~    | ~   | ~   | ~    |

| 2.5V I/O           | 2.5V UD 1.8V | ~    | ~   | ~   | ~    |

|                    | 2.5V         | ~    | ~   | ~   | ~    |

|                    | 2.5V OD 3.3V | ~    | ~   | ~   | ~    |

| SRAM               | SP           | ~    | ~   | ~   | ~    |

|                    | DP           | ~    | ~   | ~   | ~    |

*See e.g.*, https://www.chipworks.com/about-chipworks/overview/blog/review-tsmc-28-nm-process-technology.

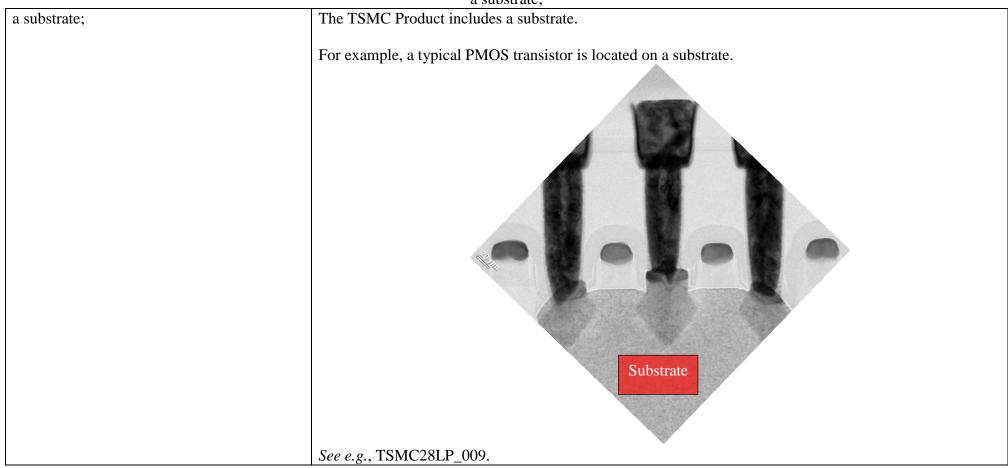

# Case 1:19-cv-00308-MN Document 1 10. 7, 100, 22/13/19 | Page 8 of 17 Page ID #: 190 "a substrate;"

### Case 1:19-cv-00308-MN Document 1-10 7-jiled 202/13/119 1-Page 9 of 17 PageID #: 191

" a plurality of transistors formed on the substrate, each transistor comprising source/drain regions and a gate electrode, having an upper and side surfaces, over the substrate with a gate dielectric layer therebetween, the gate electrodes being separated by a gap;"

a plurality of transistors formed on the substrate, each transistor comprising source/drain regions and a gate electrode, having an upper and side surfaces, over the substrate with a gate dielectric layer therebetween, the gate electrodes being separated by a gap;

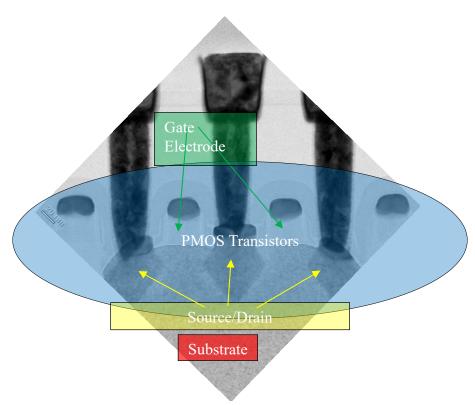

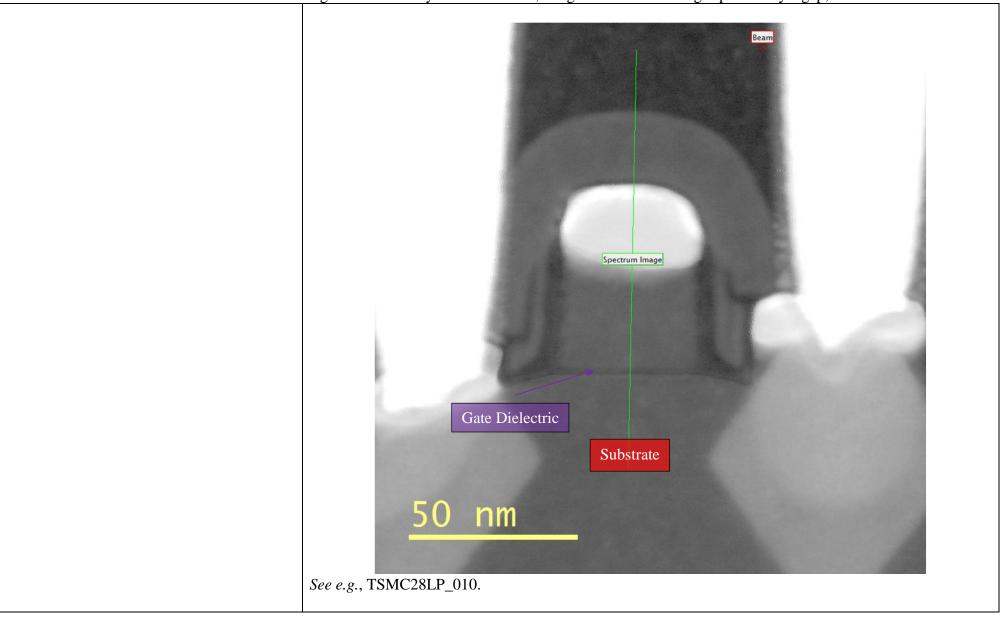

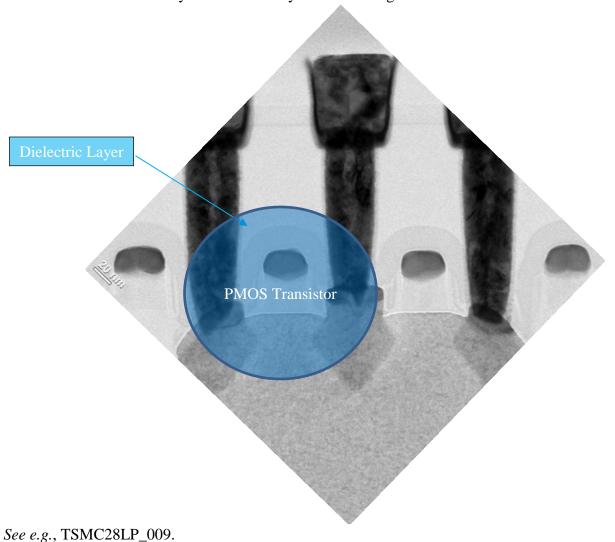

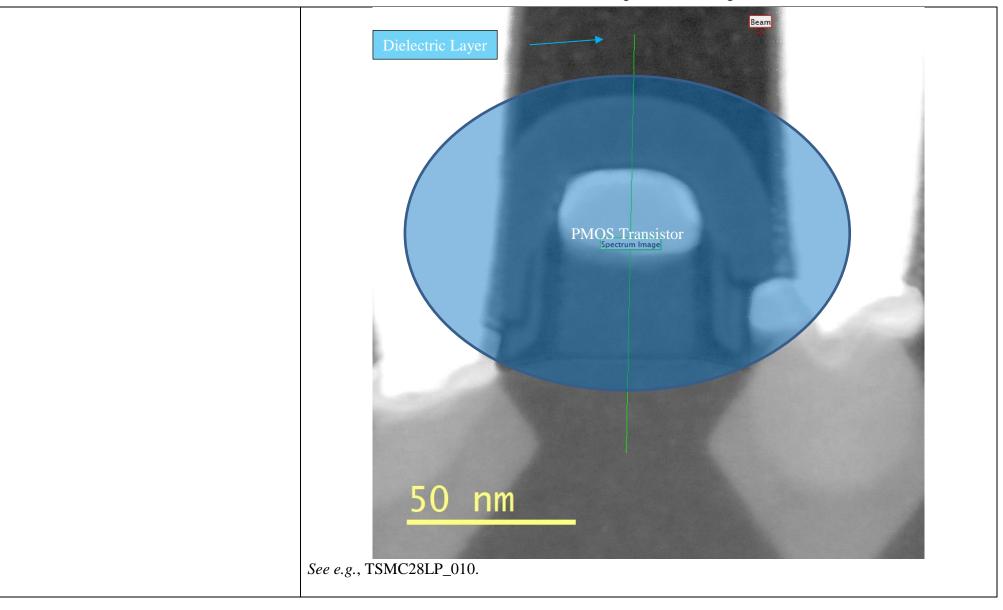

The TSMC Product includes a plurality of transistors formed on the substrate, each transistor comprising source/drain regions and a gate electrode, having an upper and side surfaces, over the substrate with a gate dielectric layer therebetween, the gate electrodes being separated by a gap.

For example, the Qualcomm Chip includes multiple PMOS transistors that include source/drain regions and gate electrodes. Typical PMOS transistors as used in the Qualcomm Chip are pictured below. The PMOS transistors are formed over the substrate and include source/drain regions and gate electrodes with upper and side surfaces. The gate electrodes are separated by a gap.

See e.g., TSMC28LP\_009.

The transistors formed on the substrate with a gate dielectric layer therebetween. For example, the Qualcomm Chip includes transistors that are formed on the substrate and separated from the substrate by a gate dielectric. Electron Energy Loss Spectroscopy (EELS) samples along the gate region show the presence of Si and O in the gate dielectric as reflected by the below diagram.

# Case 1:19-cv-00308-MN Dogument 10. Filed, 92612/12m Page 10 of 17 PageID #: 192

" a plurality of transistors formed on the substrate, each transistor comprising source/drain regions and a gate electrode, having an upper and side surfaces, over the substrate with a gate dielectric layer therebetween, the gate electrodes being separated by a gap;"

# Case 1:19-cv-00308-MN Dogument 10. Filed, 92612/12m Page 11 of 17 PageID #: 193

" a plurality of transistors formed on the substrate, each transistor comprising source/drain regions and a gate electrode, having an upper and side surfaces, over the substrate with a gate dielectric layer therebetween, the gate electrodes being separated by a gap;"

# Case 1:19-cv-00308-MN Dogument 10. Filed, 92/12/12m Page 12 of 17 PageID #: 194

" a conformal stressed nitride liner over the upper and side surfaces of the gate electrodes and over the source/drain regions; and "

| a conformal stressed nitride liner over the    |

|------------------------------------------------|

| upper and side surfaces of the gate electrodes |

| and over the source/drain regions; and         |

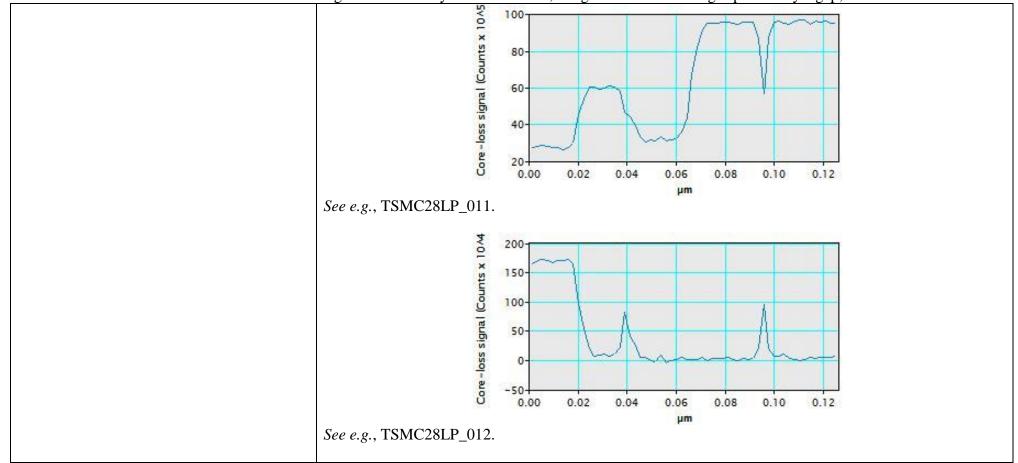

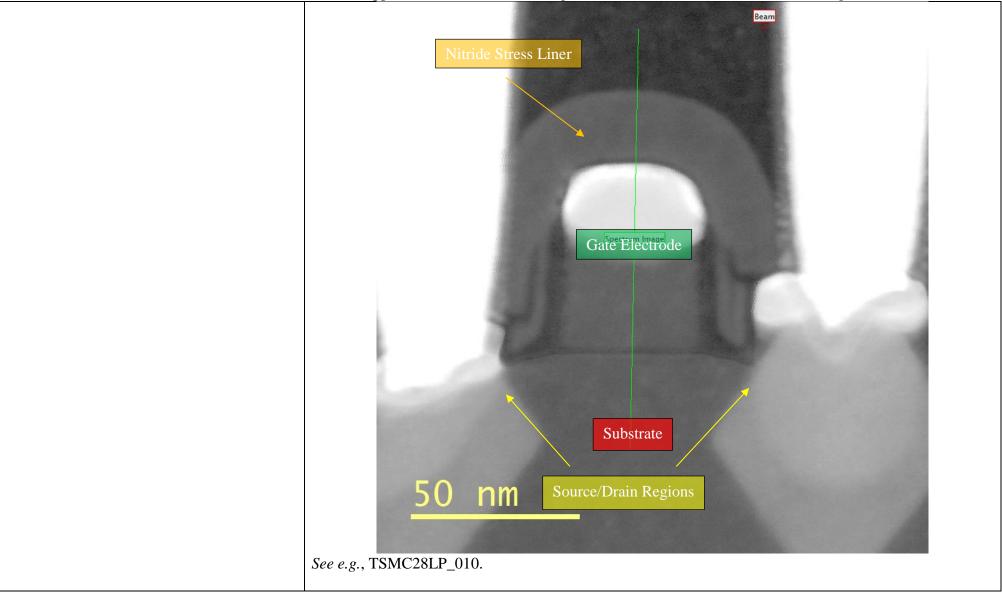

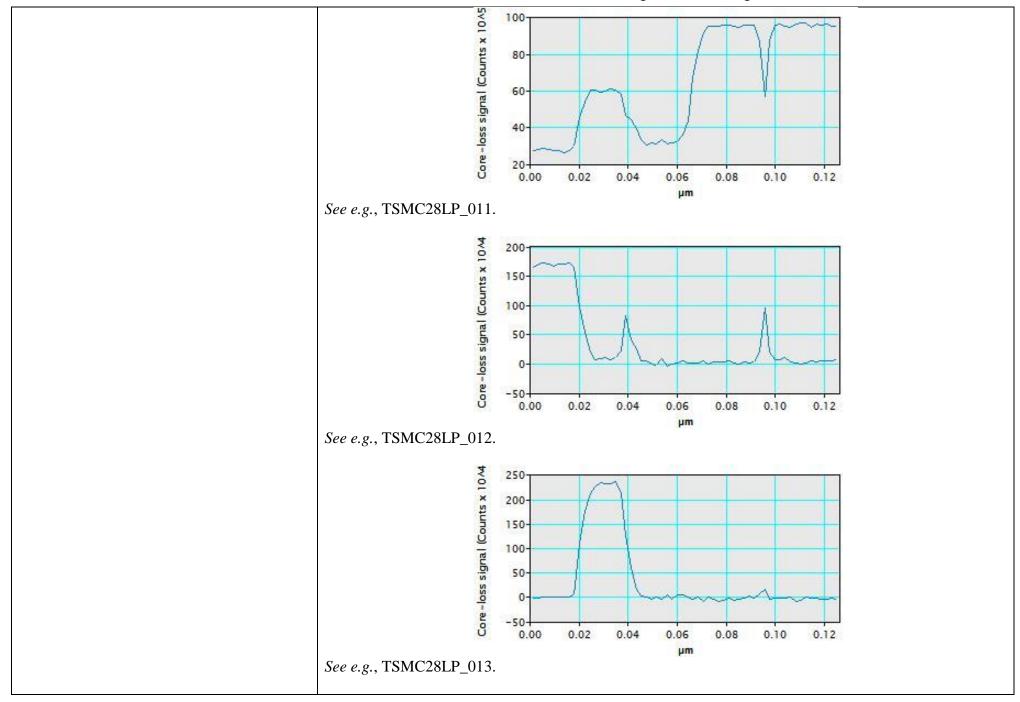

The TSMC Product comprises a conformal stressed nitride liner over the upper and side surfaces of the gate electrodes and over the source/drain regions.

For example, the Qualcomm Chip includes a PMOS transistor that further includes a conformal stressed nitride liner. The conformal stressed nitride liner is over the upper and side surfaces of the gate electrodes and over the source/drain regions. Electron Energy Loss Spectroscopy (EELS) samples along the stress liner region show the presence of N and Si in the stress liner as reflected by the below diagram.

# Case 1:19-cv-00308-MN Dogument 1, 10. Find, 02612/12/12m Page 13 of 17 PageID #: 195

" a conformal stressed nitride liner over the upper and side surfaces of the gate electrodes and over the source/drain regions; and "

# Case 1:19-cv-00308-MN Dogument 10. Filed, 92/12/12m Page 14 of 17 PageID #: 196

" a conformal stressed nitride liner over the upper and side surfaces of the gate electrodes and over the source/drain regions; and " Core-loss signal (Counts x 10.45 80 60 0.08 0.10 0.12 0.00 0.02 0.04 0.06 See e.g., TSMC28LP\_011. Core -loss signal (Counts x 10.44 200 150 100-50-0.00 0.02 0.04 0.06 0.08 0.10 0.12 μm See e.g., Qualcomm TSMC28LP\_012. Core-loss signal (Counts x 10<sup>A</sup> 250 200-150-100-50-0.00 0.02 0.04 0.12 0.06 0.08 0.10 μm See e.g., Qualcomm TSMC28LP\_013.

Page 13 of 16

a dielectric layer over the transistors and filling the gaps between the gate electrodes.

The TSMC Product comprises a dielectric layer over the transistors and filling the gaps between the gate electrodes.

For example, the Qualcomm Chip includes a dielectric layer over the transistors and filling the gaps between the gate electrodes. For example, EELS samples along the dielectric layer show the presence of Si and O in the dielectric layer as reflected by the below diagram.

Page 16 of 16